식각기술

| 기술명 | TSV (Through Silicon Via) 식각공정 기술 | ||

|---|---|---|---|

| 요약 | ㆍ Lithography의 한계성과 소형화에 따른 고집적, 고밀도의 반도체 제조를 위해 TSV (Through Silicon Via) 3D 적층 패키지 기술이 필요. ㆍ 기존 와이어 본딩 패키지나 플립칩 패키지에 비해 전력손실 적고, 동작속도 빠름 ㆍ Si Etch를 통한 Hole 및 Via 형성과 Hole 및 Via에 Seed Metal 증착의 Step Coverage 그리고 Cu전기도금을 이용한 Hole 및 Via의 Cu 충진이 중요 이슈 |

||

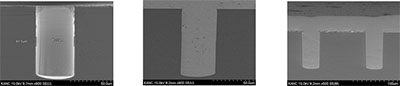

| 결과 | ㆍDiameter 약 45㎛, Depth 약 90㎛ TSV 공정 성공 - Dry Etch 공정으로 Hole 형성 - Hole측벽의 scallop의 크기를 작게하기 위한 공정 (Deposition 및 Wet Treatment) - Hole의 Bottom과 Side Wall에 Seed Metal 증착 공정 - Seam과 Void가 없는 Cu Plating 공정 * Diameter 및 Depth 크기 협의 후 공정 가능 |

||

| 사진 |

|

||

| 기술적가치 | ㆍ 고집적 가능한 반도체 소자로 성능 향상 ㆍ 모바일기기의 배터리 소모 감소 ㆍ 전력소실 최소화 |

||

| 활동분야 | ㆍ 메모리소자 등 각종 반도체 소자 ㆍ 모바일기기 |

||

| 기술관련문의 | ㆍ 시스템반도체공정개발실 이동근 선임 (031-546-6322, dongkeun.lee@kanc.re.kr) | ||